Is Non Ecc Registered Ram Compatibility

Two 8 GB DDR4-2133 ECC 1.2 V registered DIMMs (RDIMMs)

Registered (also called buffered) retentivity modules have a register betwixt the DRAM modules and the system's retentiveness controller. They place less electric load on the retention controller and permit unmarried systems to remain stable with more memory modules than they would take otherwise. When compared with registered memory, conventional memory is usually referred to as unbuffered memory or unregistered memory. When manufactured as a dual in-line memory module (DIMM), a registered memory module is called an RDIMM, while unregistered memory is called UDIMM or simply DIMM.

Registered retention is often more than expensive because of the lower number of units sold and boosted circuitry required, then it is commonly found only in applications where the need for scalability and robustness outweighs the demand for a depression toll – for instance, registered memory is unremarkably used in servers.

Although virtually registered retentiveness modules also characteristic error-correcting code retentivity (ECC), it is also possible for registered memory modules to non exist error-correcting or vice versa. Unregistered ECC retentiveness is supported and used in workstation or entry-level server motherboards that do non support very large amounts of memory.[1]

Performance [edit]

Normally, there is a operation penalty for using registered memory. Each read or write is buffered for one cycle betwixt the memory bus and the DRAM, so the registered RAM can be thought of as running one clock cycle behind the equivalent unregistered DRAM. With SDRAM, this simply applies to the first cycle of a burst.

Nevertheless, this performance penalty is not universal. There are many other factors involved in retention admission speed. For example, the Intel Westmere 5600 series of processors access retentivity using interleaving, wherein retentivity access is distributed beyond 3 channels. If 2 retentivity DIMMs are used per aqueduct, this "results in a reduction of maximum memory bandwidth for 2DPC (DIMMs per channel) configurations with UDIMM past some 5% in comparing to RDIMM".[ attribution needed ] [ii] (p. 14). This occurs because "when you get to two DIMMs per retentivity channel, due to the high electrical loading on the address and control lines, the memory controller uses a '2T' or '2N' timing for UDIMMs. Consequently, every command that unremarkably takes a single clock cycle is stretched to 2 clock cycles to permit for settling time.

Compatibility [edit]

Usually, the motherboard must match the memory type; as a result, registered memory will non work in a motherboard non designed for information technology, and vice versa. Some PC motherboards accept or require registered memory, but registered and unregistered memory modules cannot exist mixed.[3] In that location is much defoliation betwixt registered and ECC retentivity; it is widely thought that ECC memory (which may or may not be registered) will not work at all in a motherboard without ECC support, non fifty-fifty without providing the ECC functionality, although the compatibility issues really arise when trying to employ registered memory (which also supports ECC and is described equally ECC RAM) in a PC motherboard that does not support it.

Buffered retentiveness types [edit]

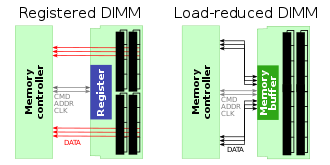

Comparison: Registered Retention (R-DIMM) and Load Reduced DIMM (LR-DIMM)[four]

Registered (Buffered) DIMM (R-DIMM) modules insert a buffer between the pins of the control and address buses on the DIMM and the memory chips. A high-capacity DIMM might have numerous memory chips, each of which must receive the memory address, and their combined input capacitance limits the speed at which the memory coach tin operate. Past redistributing the command and address signals inside the R-DIMM, this allows more fries to be connected to the memory charabanc.[5] The cost is increased memory latency, as a result of one[ citation needed ] additional clock cycle required for the address to traverse the additional buffer. Early registered RAM modules were physically incompatible with unregistered RAM modules, but the two variants of SDRAM R-DIMMs are mechanically interchangeable, and some motherboards may support both types.[ citation needed ]

Load Reduced DIMM (LR-DIMM) modules are like to R-DIMMs, but add together a buffer to the data lines as well. In other words, LR-DIMMs buffer both control and data lines while keeping the parallel nature of all signals. Equally a result, LR-DIMMs provides big overall maximum retention capacities, while avoiding the operation and power consumption problems of FB-DIMMs, induced by the required conversion betwixt serial and parallel signal forms.[5] [6]

Fully Buffered DIMM (FB-DIMM) modules increase maximum memory capacities in large systems even more than, using a more circuitous buffer bit to translate between the wide omnibus of standard SDRAM chips and a narrow, high-speed serial memory coach. In other words, all command, accost and data transfers to FB-DIMMs are performed in a serial way, while the additional logic nowadays on each FB-DIMM transforms serial inputs into parallel signals required to bulldoze memory chips.[6] By reducing the number of pins required per retentiveness coach, CPUs could support more memory buses, allowing college total memory bandwidth and capacity. Unfortunately, the translation further increased retentiveness latency, and the circuitous high-speed buffer fries used significant power and generated a lot of heat.

Both FB-DIMMs and LR-DIMMs are designed primarily to minimize the load that a memory module presents to the memory autobus. They are not compatible with R-DIMMs, and motherboards that require them normally will not take whatsoever other kind of memory modules.

References [edit]

- ^ "Servers and workstations: P9D-V motherboard". Asus. Retrieved December four, 2014.

- ^ "Archived copy" (PDF). Archived from the original (PDF) on 2014-05-29. Retrieved 2012-10-28 .

{{cite web}}: CS1 maint: archived copy as title (link) - ^ "Dell servers example" (PDF). Dell.

- ^ Deffree, Suzanne (September 20, 2011). "Basics of LRDIMM". EDN. Archived from the original on April 2, 2021.

- ^ a b Johan De Gelas (2012-08-03). "LRDIMMs, RDIMMs, and Supermicro'due south Latest Twin". AnandTech. Retrieved 2014-09-09 .

- ^ a b "What is LR-DIMM, LRDIMM Memory? (Load-Reduce DIMM)". simmtester.com . Retrieved 2014-08-29 .

External links [edit]

- Memory Decisions Archived 2019-05-19 at the Wayback Machine, February viii, 2004

- Do I Need ECC and Registered Memory (.md document)

- Basics of LRDIMM

- LRDIMM vs RDIMM: Indicate integrity, chapters, bandwidth

Is Non Ecc Registered Ram Compatibility,

Source: https://en.wikipedia.org/wiki/Registered_memory

Posted by: youngpois1945.blogspot.com

0 Response to "Is Non Ecc Registered Ram Compatibility"

Post a Comment